MCU는 STM32F030F4P6을 사용하였고 관련 데이터 시트는 아래 첨부했습니다.

ADC 설정 개념

1. Mode

ADC 하나에는 여러 채널이 있다.

위 그림을 보면 9개의 채널과 내부적으로 연결된 2개의 채널이 있는 것을 확인할 수 있다.

EXTI Conversion Trigger는 ADC의 값이 변환되면 Trigger를 발생시키겠다는 것이다.

2. Configuration - Parameter Settings

① ADCs_Common_Settings

Mode: Independent Mode

ADC1, ADC2가 독립적으로 작동할 경우 사용되는 모드

② ADC_Settings

ⓐ Clock Prescaler

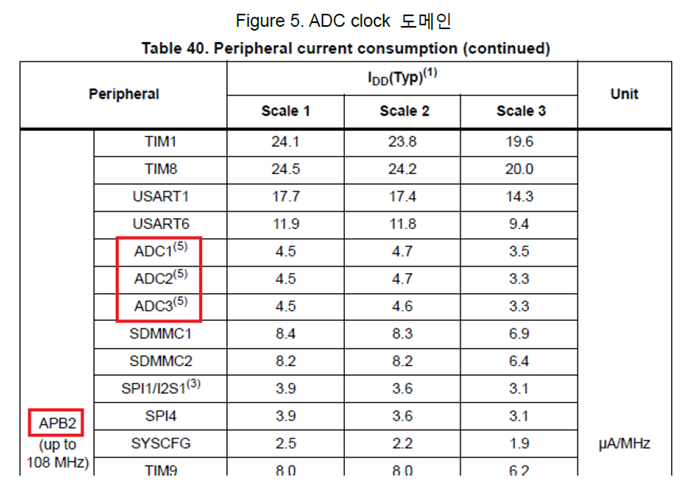

사용하려는 ADC peripheral의 최대속도(fADC)와 어느 clock 도메인(APB1, APB2, APB3)에 속해 있는지 데이터시트를 통해 확인한다.

일부 최신 STM32디바이스는ADC peripheral clock 소스로 AHB에서 /1,/2,/4를 하는 synchronous clock 설정과 ADC Clock Mux에서 /1,/2,../128,/256을 하는 asynchronous clock 설정을 대신 제공한다.

APBx clock을 사용하는 MCU의 경우 사용자가 설정한 HCLK 설정에 따라 APBx Clock의 속도도 같이 바뀌기 때문에 설정된 APBx(PCLKx) clock 주파수를 ADC 내부의 prescaler로 나눈 최종 ADC peripheral clock 속도를 계산한다. (아래 예시 108 MHz / 4 = 27 MHz)

ADC 내부의 prescaler값은 모든 ADC block (ADC1, ADC2, ADC3)에 공통 적용되는 내용이므로 ADC1에서 /4를 선택하면ADC2, ADC3도 /4로 바뀌는 점에 유의한다.

ⓑ Resolution(분해능)

해상도와 같은 개념이다.

ADC는 3bit, 8bit, 10bit, 12bit가 있는데 샘플링 간격은 저장용량 및 전송용량과 같다.

예를 들어 3bit ADC는 적은 용량을 사용하고 샘플링 및 양자화하는 간격이 넓다. 따라서 오차가 크다.

하지만 12bit ADC는 많은 용량을 사용하지만 샘플링 및 양자화하는 간격이 좁아서 오차가 적고 아날로그에 가깝다.

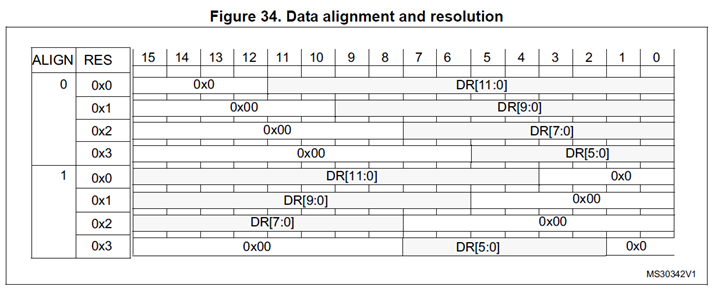

ⓒ Data Alignment

결과 값을 16bit 레지스터에 저장할 때 12bit 결과 값이 오른쪽에서부터 저장할건지 왼쪽에서부터 저장할건지 설정하는 곳이다.

위 그림처럼 ALIGN = 0은 오른쪽에서부터 저장, ALIGN = 1은 왼쪽에서부터 저장한 예시이다.

ⓓ Scan Conversion Mode

여러 개의 아날로그 채널에서 입력 받을 경우, 순차적으로 샘플링하는 모드로 DMA와 함께 사용하는 것이 일반적이다.

그리고 forward, backward 중에서 설정이 가능하다.

예를 들어 forward이고, 채널이 2,3,4번이 설정되었다면 2번이 끝나면 자동으로 3번, 4번으로 넘어가면서 Conversion한다.

ⓔ Continuous Conversion Mode

연속적으로 샘플링을 계속 수행하는 모드로 전체 채널을 샘플링하고 멈추지 않고 계속 수행한다.

Injected group에서는 사용할 수 없다. 만약 이 모드가 Disable이면 하나의 conversion이 끝나면 멈춘다.

그리고 다시 시작하라는 명령이 들어와야 다시 시작한다. Enable이면 자동으로 계속 conversion한다.

※ Regular conversion mode와 Injected conversion mode

선택한 ADC 채널을 Regular group 혹은 Injected group로 설정할 수 있다.

이 두 그룹의 차이점은 Injected 모드로 설정한 채널에서 ADC 시작 트리거가 발생하면 현재 진행 중이었던 ADC 샘플링을 중단시키고 강제로 Injected 모드의 채널의 ADC 샘플링을 시작한다.

ⓕ Discontinuous Conversion Mode

불연속적으로 샘플링을 수행하는 모드로 전원 절약을 목적으로 주로 사용된다.

Regular group에 할당된 전체 채널을 conversion하는 것이 아니라 일부만 요청한다.

예를 들어 Regular group에 채널 1,2,3,4,5,6이 할당되어 있고, discontinuous mode를 사용하면서 값을 2로 설정하면 처음에는 1,2 그 다음에 3,4 그 다음에 5,6 이렇게 동작한다.

ⓖ DMA Continuous Requests

이 매개변수는 DMA 요청이 구성된 경우에만 사용된다.

이 ADC 객체에 대한 DMA 요청 시 이 매개변수는 DMA 요청이 일회성 모드(변환 횟수에 도달하면 DMA 전송이 중지됨)에서 수행되는지 아니면 연속 모드(변환 횟수에 관계없이 무제한 DMA 전송)에서 수행되는지 여부를 지정한다.

참고: 연속 모드에서는 DMA를 순환 모드로 구성해야 한다. 그렇지 않으면 DMA 버퍼 최대 포인터에 도달할 때 오버런이 트리거 된다.

ⓗ End Of Conversion Selection

한 채널의 conversion을 마치고 EOC Flag를 넣어줄 건지, 모든 채널의 conversion을 마치고 EOC Flag를 넣어줄 건지 결정한다.

ⓘ Overrun behavior

오버런 되었을 때 그 데이터를 보존할 건지, 덮어쓸 건지 결정한다.

ⓙ Low Power Auto Wait

동적 저전력 자동 지연의 사용을 지정한다.

이전 conversion(일반 채널의 경우)이 완료된 경우에만 새로운 conversion이 시작된다.

ⓚ Low Power Auto Power Off

자동 꺼짐 모드를 활성화 또는 비활성화한다.

ADC는 변환 후 자동으로 전원이 꺼지고 새 변환이 트리거되면 자동으로 깨어난다.

③ ADC_Regular_ConversionMode

Regular_ConversionMode는 레지스터가 1개이다.

만약 conversion의 개수를 2개로 위와 같이 설정한다면 첫 번째는 Rank1의 2번 채널을 conversion하고 두 번째는 Rank2의 4번 채널을 conversion한다.

그런데 레지스터가 1개이기 때문에 4번 채널을 conversion하고 나면 2번 채널에 conversion했던 정보가 덮어써진다.

그래서 폴링방식이 아니면 사용할 수 없다.

즉 내가 순차적으로 불러서 1번이 끝나면 데이터를 확인하고 난 후 어떤 작업을 하고 그 다음 수동으로 2번으로 넘어가는 방식으로 동작하지 않으면 레지스터 1개를 공유해서 사용하기 때문에 내가 읽어온 정보가 1번인지 2번인지 그 순간 타이밍에 알 수 없다.

ⓐ External Trigger Conversion Source

언제 Conversion을 시작할건지에 대한 정보이다.

소프트웨어로 제어한다면 소프트웨어로 특정 레지스터에 값을 써주면 conversion을 시작하는 구조이다.

나머지 옵션들은 타이머를 사용한다.

타이머는 어떤 조건이 되면 소프트웨어로 알리지 않아도 자동으로 conversion을 시작하도록 구조를 만들고 싶을 때 사용한다.

ⓑ Sampling Time

CPU의 사이클을 얼마나 사용할건지에 대한 정보이다.

너무 짧으면 노이즈에 약하고 길면 CPU 사이클을 많이 사용한다.

적절한 사이클은 데이터시트를 참고하면 된다.

④ ADC_Injected_ConversionMode

Injected_ConversionMode는 레지스터가 4개이지만 conversion 개수가 최대 4개까지만 가능하다.

⑤ WatchDog

인터럽트를 발생시킨다고 생각하면 된다.

위와 같이 조건을 설정했다고 한다면 채널 2번을 conversion한 값이 3000을 넘어가거나 1000 아래로 떨어지면 인터럽트가 발생된다.

3. Configuration - NVIC Settings

Global 인터럽트를 발생시키고자 하면 Enable하면 되는데 여기에 해당되는 인터럽트는 다양한 종류가 있다.

① OVR(Overrun Interrupt)

ADC 결과 데이터를 읽지 않고 다시 샘플링을 시작할 경우 발생하는 인터럽트로 결과 데이터의 최신성을 보장한다.

② EOC(End of Conversion Interrupt)

ADC 각각의 채널에 대한 샘플링이 완료되었을 때 발생하는 인터럽트이다.

③ JEOC(Injected End of Conversion Interrupt)

ADC Injected 그룹에 대한 샘플링이 완료되었을 때 발생하는 인터럽트이다.

④ AWD(Analog Watchdog Interrupt)

ADC에서 측정한 아날로그 전압이 설정된 하한 값 또는 상한 값을 벗어났을 때 발생하는 인터럽트이다.

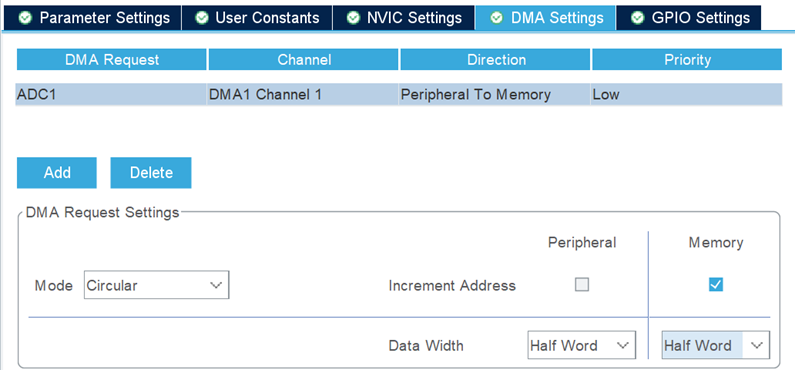

4. Configuration - DMA Settings

폴링방식은 매번 값이 변했는지 확인하고 변한 값을 특정 메모리로 복사하는 과정을 수동으로 해야 한다.

즉 CPU파워를 쓴다.

그런데 DMA는 ADC값이 어떤 결과가 나오면 CPU파워를 쓰지 않고 자동으로 DMA 특정 메모리에 기록을 해버린다.

결론적으로 CPU가 관여하지 않기 때문에 고속처리에 용이하다. 그래서 대부분 ADC를 사용한다고 하면 DMA를 설정한다.

① Mode

Normal은 conversion이 끝나면 한번 저장하고 끝내지만 Circular는 지속적으로 저장한다.

② Data Width

Byte는 8bit, Half Word는 16bit, Word는 32bit이다.

여기서는 12bit ADC를 사용하므로 16bit인 Half Word로 설정하면 된다.

③ Memory 체크

만약 채널이 4개이고 메모리에 체크를 안 하면 한 메모리에 기록하고 덮어쓴다.

하지만 체크를 하면 위의 그림처럼 각각에 메모리에 기록한다.

④ Peripheral 체크

Peripheral에 체크가 되어 있지 않으면 ADC1의 4개 채널만을 반복적으로 기록한다.

하지만 체크가 되어 있다면 ADC1의 4개 채널을 기록한 뒤 ADC2로 넘어가서 4개 채널을 기록한다.

ADC 설정 실전

1. Parameter Settings

① ADC_Settings

ⓐ Clock Prescaler

● ADC peripheral의 최대 속도(fADC) 찾기

STM32F030F4P6_Reference Manual (p187~188)

12.4.3 ADC clock (CKMODE)

ADC에는 dual clock 도메인 아키텍처가 있으므로 APB clock(PCLK)과 독립적인 clock(ADC 비동기 clock)을 ADC에 공급할 수 있습니다.

아날로그 ADC의 입력 clock은 두 개의 서로 다른 clock 소스 중에서 선택할 수 있습니다.

(PCLK 및 ADC 비동기 clock이 활성화되는 방법을 보려면 Figure 26: ADC clock 구성표 참조):

a) ADC clock은 APB clock과 독립적이고 비 동기적인 "ADC 비동기 clock"이라는 특정 clock 소스일 수 있습니다. 이 clock 소스 생성에 대한 자세한 내용은 RCC 섹션을 참조하세요. 이 방식을 선택하려면 ADC_CFGR2 레지스터의 CKMODE[1:0] 비트를 재설정해야 합니다.

코드 예는 부록 섹션 A.7.4: ADC clock 선택 코드 예를 참조하세요.

b) ADC clock은 ADC 버스 인터페이스의 APB clock에서 파생될 수 있으며 비트 CKMODE[1:0]에 따라 프로그래밍 가능한 요소(2 또는 4)로 나뉩니다. 이 방식을 선택하려면 ADC_CFGR2 레지스터의 CKMODE[1:0] 비트가 "00"과 달라야 합니다.

옵션 a)는 선택한 APB clock 구성표에 관계없이 최대 ADC clock 주파수에 도달할 수 있다는 장점이 있습니다.

옵션 b)는 clock 도메인 재동기화를 우회하는 장점이 있습니다. 이는 ADC가 타이머에 의해 트리거 될 때 그리고 애플리케이션에서 ADC가 불확실성 없이 정확하게 트리거 되어야 하는 경우에 유용할 수 있습니다(그렇지 않으면 두 clock 도메인 간의 재동기화로 인해 트리거 순간의 불확실성이 추가됩니다).

※ Jitter

신호의 주기, 주파수, 위상, duty cycle, 또는 다른 타이밍 특성 등의 불안정성을 나타낸다.

※ Clock cycle

Clock의 시간 간격을 나타낸다.

예를 들어 12MHz의 주파수는 1초에 12,000,000번 clock이 뛴다.

따라서 1/12,000,000을 하면 clock이 1번 뛰는데 걸리는 시간이 나온다. 이 경우에는 약 0.08us이다.

그런데 위의 표에서 2.75 clock cycle의 지연시간이 발생한다는 뜻은 2.75 * 0.08us의 지연시간을 의미하며 이는 0.22us이다.

즉, 0.22us의 지연시간이 발생할 수 있다는 뜻이다.

● 어느 clock 도메인(APB1, APB2, APB3 등)에 속해 있는지 찾기

STM32F030F4P6_Reference Manual (p40) - Memory map and register boundary address

● 결론

Asynchronous clock mode

APB clock 구성표에 관계없이 최대 ADC clock 주파수인 14MHz로 Clock Prescaler을 설정하겠다.

다만 불안정성이 있다.

Synchronous clock mode divided by 4

ADC가 속해있는 APB clock(48MHz)을 4로 나눈 12MHz로 Clock Prescaler을 설정하겠다.

다만 2.625 clock cycle(0.21us)의 지연시간이 있지만 불안정성은 없다.

여기서는 Asynchronous clock mode를 선택했다.

ⓑ Resolution

ADC-12bit resolution

ⓒ Data Alignment

Right alignment로 설정

결과 값을 16bit 레지스터에 저장할 때 12bit 결과 값이 오른쪽에서부터 저장하겠다.

ⓓ DMA Continuous Requests

DMA를 사용하겠다.

② ADC_Regular_ConversionMode

ⓐ Sampling Time

STM32F030F4P6_Reference Manual.pdf의 12.2, 12.4.6에 ADC Conversion time은 12bit-resolution일 경우 1.0us이고, ADC Conversion time은 sampling time + 12.5 x ADC clock cycles라고 나와 있다.

여기서 ADC는 14MHz이므로 ADC clock cycles은 1/14,000,000 = 0.0714us

Sampling time은 1.5 cycle을 선택했을 때 1.5 x 0.0714 = 0.107us

따라서 ADC Conversion time = sampling time + 12.5 x ADC clock cycles (14MHz) 이므로

ADC Conversion time = 0.107us + 0.892us = 약 1.0us이다.

결론적으로 sampling time은 최소 1.5 cycle 이상부터 선택할 수 있다.

ⓑ External Trigger Conversion Source

소프트웨어로 특정 레지스터에 값을 써서 conversion을 시작하겠다.

2. DMA Settings

① Mode

Normal로 설정하여 conversion이 끝나면 한번 저장하고 끝내겠다.

② Data Width

여기서는 12bit ADC를 사용하므로 Half Word로 설정하여 16bit를 사용하겠다.

③ Memory 체크 해제

그림의 왼쪽처럼 한 메모리에 기록하고 덮어쓰겠다.

④ Peripheral 체크 해제

여기서는 ADC1, ADC2가 있지 않고 ADC가 유일하다.

따라서 ADC의 채널만을 반복적으로 기록하겠다.

'개발환경 > STM32CubeMX' 카테고리의 다른 글

| GPIO(LED) 설정 - STM32F030F4P6 (0) | 2023.11.18 |

|---|---|

| Debug 설정 - STM32F030F4P6 (1) | 2023.11.18 |

| UART(RS-485) 설정 - STM32F030F4P6 (1) | 2023.11.18 |

| 타이머 설정 - STM32F030F4P6 (1) | 2023.11.18 |

| Clock 설정 - STM32F030F4P6 (0) | 2023.11.18 |