MCU는 NUC029SGE를 사용하였고 관련 데이터 시트는 아래 첨부했습니다.

코드 분석

static void sSysClk_Init(void)

{

//Unlock protected registers

SYS_UnlockReg();

/* Disable clock source */

CLK_DisableXtalRC(CLK_PWRCTL_HXTEN_Msk);

if(!(CLK->STATUS & CLK_STATUS_HXTSTB_Msk)) {

SYS->GPF_MFPL &= ~(SYS_GPF_MFPL_PF3MFP_Msk | SYS_GPF_MFPL_PF4MFP_Msk);

SYS->GPF_MFPL |= (SYS_GPF_MFPL_PF3MFP_GPIO | SYS_GPF_MFPL_PF4MFP_GPIO);

}

/* Enable HIRC clock (Internal RC 22.1184MHz) */

CLK_EnableXtalRC(CLK_PWRCTL_HIRCEN_Msk);

/* Waiting for HIRC clock ready */

CLK_WaitClockReady(CLK_STATUS_HIRCSTB_Msk);

/* Enable HIRC clock (Internal RC 48MHz) */

CLK_EnableXtalRC(CLK_PWRCTL_HIRC48EN_Msk);

/* Waiting for HIRC clock ready */

CLK_WaitClockReady(CLK_STATUS_HIRC48STB_Msk);

CLK_SetSysTickClockSrc(CLK_CLKSEL0_STCLKSEL_HIRC_DIV2);

/* Set HCLK clock source and HCLK clock divider */

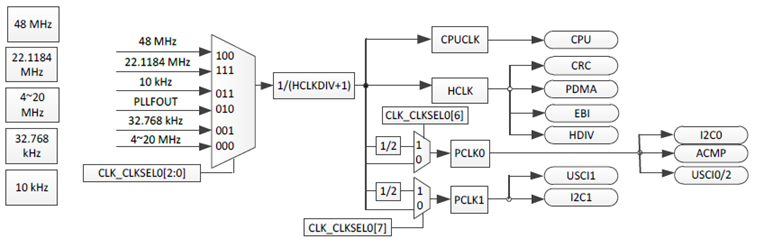

CLK_SetHCLK(CLK_CLKSEL0_HCLKSEL_HIRC, CLK_CLKDIV0_HCLK(1));

/* User can use SystemCoreClockUpdate() to calculate PllClock, SystemCoreClock and CyclesPerUs automatically. */

SystemCoreClockUpdate();

//Lock protected registers

SYS_LockReg();

}

1) CLK_DisableXtalRC(CLK_PWRCTL_HXTEN_Msk);

4~20MHz External High Speed Crystal (HXT)을 비활성화 하겠다는 뜻이다.

이것은 MCU에서 사용되는 외부 크리스털로, MCU의 시스템 클럭을 생성하는 데 사용됩니다.

2) If문

if(!(CLK->STATUS & CLK_STATUS_HXTSTB_Msk)) {

SYS->GPF_MFPL &= ~(SYS_GPF_MFPL_PF3MFP_Msk | SYS_GPF_MFPL_PF4MFP_Msk);

SYS->GPF_MFPL |= (SYS_GPF_MFPL_PF3MFP_GPIO | SYS_GPF_MFPL_PF4MFP_GPIO);

}

if(!(CLK->STATUS & CLK_STATUS_HXTSTB_Msk)) {

HXTSTB가 0이면 if문을 실행하겠다.

= 4~20 MHz External High Speed Crystal (HXT) 꺼져있다면, if문을 실행하겠다는 뜻이다.

SYS->GPF_MFPL &= ~(SYS_GPF_MFPL_PF3MFP_Msk | SYS_GPF_MFPL_PF4MFP_Msk);

SYS->GPF_MFPL |= (SYS_GPF_MFPL_PF3MFP_GPIO | SYS_GPF_MFPL_PF4MFP_GPIO);

PF3MFP, PF4MFP에 해당하는 bit를 모두 지우겠다.

그리고 해당 bit에 0을 쓰겠다.

즉 PF3, PF4번 핀을 외부 4~20MHz 외부 고속 수정 발진기(HXT) 핀이 아닌 GPIO 핀으로 구성하겠다는 뜻이다.

3) CLK_EnableXtalRC(CLK_PWRCTL_HIRCEN_Msk);

22.1184 MHz internal high speed RC oscillator (HIRC) 활성화 하겠다는 뜻이다.

※ HIRC

High-Speed Internal RC Oscillator의 약자이다.

이것은 내부적으로 생성된 고속 동작 클럭을 나타내며, 대부분의 MCU에서 기본 클럭 소스로 사용된다.

HIRC는 일반적으로 안정성이 높고, 적은 외부 부품을 필요로 하기 때문에 매우 편리합니다.

그러나, 외부 요인에 의해 영향을 받을 수 있으므로 보다 정확한 타이밍이 필요한 경우에는 외부 클럭을 사용하는 것이 좋다.

4) CLK_WaitClockReady(CLK_STATUS_HIRCSTB_Msk);

HIRCSTB는 HIRC Clock Source Stable Flag으로 값이 1이면 22.1184 MHz internal high speed RC oscillator(HIRC) clock가 안정화되고 사용할 수 있다는 뜻이다.

따라서 HIRC Clock Source Stable Flag의 값이 1이 될 때까지 기다리겠다는 뜻이다.

5) CLK_EnableXtalRC(CLK_PWRCTL_HIRC48EN_Msk);

48 MHz internal high speed RC oscillator (HIRC48) 활성화 하겠다는 뜻이다.

6) CLK_WaitClockReady(CLK_STATUS_HIRC48STB_Msk);

HIRC48STB는 HIRC48 Clock Source Stable Flag으로 값이 1이면 48 MHz internal high speed RC oscillator(HIRC) clock가 안정화되고 사용할 수 있다는 뜻이다.

따라서 HIRC48 Clock Source Stable Flag의 값이 1이 될 때까지 기다리겠다는 뜻이다.

7) CLK_SetSysTickClockSrc(CLK_CLKSEL0_STCLKSEL_HIRC_DIV2);

Systick clock source를 HIRC/2로 하겠다.

= Systick은 시스템 타이머를 구동하는데 사용되는 클럭인데, 이 클럭을 HIRC/2로 하겠다는 뜻이다.

※ SysTick 타이머와 범용 타이머

SysTick 타이머는 ARM 기반 MCU에 내장된 시스템 타이머로 시간 기반 기능을 구현하는데 사용된다.

범용 타이머는 MCU에 통합된 다재 다능한 타이머로, 다양한 타이밍 및 제어 응용 프로그램을 위해 구성할 수 있다.

대표적인 예로 특정 핀을 범용 타이머로 설정한 뒤 PWM 신호를 생성하여 모터나 LED 밝기 제어를 할 수 있다.

8) CLK_SetHCLK(CLK_CLKSEL0_HCLKSEL_HIRC, CLK_CLKDIV0_HCLK(1));

HCLK clock source는 HIRC로 하고 HCLK clock divider는 1로 하겠다.

= HCLK clock source는 HIRC를 1로 나눈 clock source를 사용하겠다는 뜻이다.

※ HCLK

High-speed Clock의 약자로, CPU와 다른 주요 하드웨어 블록들의 클럭 속도를 정의하는 중요한 매개 변수 중 하나이다.

HCLK는 CPU와 다른 하드웨어 블록들의 클럭 동기화를 유지하는 데 중요하다.

이러한 하드웨어 블록에는 외부 메모리, DMA 컨트롤러, 타이머, 시리얼 통신 인터페이스 등이 포함될 수 있다.

HCLK의 속도는 MCU의 데이터 처리 속도와 전체 시스템 성능에 직접적인 영향을 미치므로, 개발자는 HCLK의 적절한 설정을 통해 시스템의 최적화와 안정성을 달성할 수 있다.

※ HIRC, HCLK 차이점

HIRC는 고속 내부 RC 발진기를 나타내고 HCLK는 고속 클럭을 나타낸다.

HIRC는 많은 MCU에 내장된 클럭 소스이며 HCLK는 프로세서 코어 및 기타 주변 장치를 구동하는 기본 클럭 신호이다.

9) SystemCoreClockUpdate();

PllClock, SystemCoreClock 및 CyclesPerUs를 자동으로 계산하는 함수

※ PLL 클럭 또는 Phase-Locked Loop 클럭

마이크로컨트롤러 또는 기타 전자 장치의 PLL 회로에서 생성되는 클럭 신호이다.

PLL은 기준 클럭 신호를 사용하여 기준 신호와 동기화되는 더 높은 주파수 클럭 신호를 생성하는 피드백 제어 시스템이다.

기준 클럭 신호는 일반적으로 외부 수정 발진기 또는 고속 내부 RC 발진기(HIRC)와 같은 내부 발진기에서 파생된다.

PLL 회로는 기준 신호의 주파수를 곱하여 더 높은 주파수 클럭 신호를 생성하기 위해 기준 신호를 사용한다.

결론

22.1184 MHz internal high speed RC oscillator (HIRC)을 활성화

48 MHz internal high speed RC oscillator (HIRC48)을 활성화

시스템 타이머 클럭(Systick)은 HIRC/2로 사용 => 11.0592MHz

시스템 클럭(HCLK)은 HIRC/1로 사용 => 22.1184MHz

PLL Clock 외 다른 것들은 계속 업데이트 하겠다.

'개발환경 > Keil' 카테고리의 다른 글

| ADC 설정 - NUC029SGE (1) | 2023.11.18 |

|---|---|

| UART 설정 - NUC029SGE (1) | 2023.11.18 |

| 타이머 설정 - NUC029SGE (1) | 2023.11.18 |